# **Inductor Modeling of Integrated Passive Device for RF Applications**

Yuan-Chia Hsu

Chip Implementation Center

1F, No.1, Prosperity Road I,

Science-Based Industrial Park, Hsinchu

Taiwan, R.O.C.

ychsu@cic.org.tw

Meng-Lieh Sheu

Department of Electrical Engineering

National Chi Nan University

#301, University Road, Puli, Nantou

Taiwan, R.O.C.

sheu@ncnu.edu.tw

Abstract: - In this paper, an integrated passive device (IPD) inductor modeling is demonstrated. The IPD technology is a system in package (SiP) solution where passive devices with high quality can be fabricated on a chip and then connect with another circuit chip by using flip-chip micro-bump bonding. For an RF circuit simulation, the IPD inductor model is built and verified from the measurement results.

Key-Words: - integrated passive device, system in package, flip-chip, inductor modeling

### 1 Introduction

The integration of on-chip spiral inductors in CMOS process for RF applications has been the subject of many researches. In standard CMOS process, the Q factor is restricted by the metal resistance and by the substrate eddy current losses. Many technology modifications are employed to improve the Q factor [1-8]. Burghartz, et al. [1] used additional substrate contacts to improve the Q factor. Park [2] modified the internal diameter of spiral inductor layout to reduce the substrate losses. Yue [3] proposed a patterned ground between the inductor and substrate for shielding. Octangle spiral inductor and symmetrical structure were suggested by [4, 5]. Post processing, copper interconnect, and low dielectric material were demonstrated by [6, 7, 8]. Nevertheless, the ever best reported quality (Q) factors are between 10~20 [9, 10], depending on the technology. Moreover, on-chip inductor modeling is difficult and is typically limited to accuracy below

To achieve a high Q factor inductor, system in package (SiP) technology seems to be an interesting and reasonable solution. Multi-layer ceramic (MLC) and multi-chip module (MCM) are two most attractive SiP technologies. MLC technology can integrate passive devices with high Q value around 80 [11, 12], but the process cost needs to be cut. MCM technology employs lower cost flip chip packaging where passive devices with high quality can be fabricated on a chip and then connect with another circuit chip by using flip-chip micro-bump bonding [13, 14]. The passive devices fabricated can achieve a Q value higher above 50. GaAs MMIC and silicon component had been integrated together by MCM technology for RF application [15].

CMOS chips and passive devices integrated by MCM technology for RF applications were also reported in [16, 17].

Circuit simulations with accurate models are the success key for RFIC designers. For CMOS process technologies after 0.25um, the manufacturer would provide RF models for transistors and on-chip spiral inductors. The transistor models have no choice but to be used. Nonetheless, aside from the lower Q factor, the on-chip inductor models are typically limited to accuracy below 10%. Domestic manufacturer [18] supports MCM packaging as well as high O inductors fabricated by integrated passive device (IPD) technology. Hence, in this paper, to use the IPD inductor for CMOS RFIC designs, the IPD inductor models are built and verified from the measurement results. The models are used in designing a cascode LNA employing IPD inductors. The simulation results show its superiority when compared with conventional on-chip inductor LNA.

## 2 Inductor Modeling

In this section, the flow to build an inductor model is described step by step and illustrated by an example. The example is a 2.5-turn on-chip rectangular spiral inductor fabricated by 0.25  $\mu m$  1P5M CMOS process.

#### 2.1 Modeling Steps

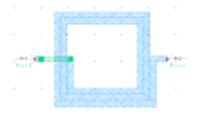

The first step is to choose the desired inductor to be modeled. A 2.5-turn on-chip rectangular spiral inductor is chosen, and its layout is shown in Fig.1. Some physical parameters of the process, including the thickness of metal layer and oxide layer, the

dielectric constant, etc., are required to perform an electromagnetic simulation by using Agilent's ADS. The distribution of electromagnetic field of the inductor would be calculated and analyzed. From these analysis and calculations, a set of S parameters will be derived.

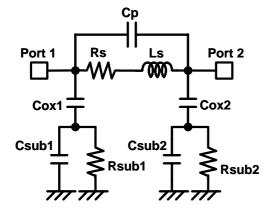

The second step is to construct an equivalent circuit based on the layout and inductor structure. A corresponding equivalent circuit [19] is shown in Fig.2.  $L_s$  and  $R_s$  are the series inductor and resistor.  $C_p$  is the capacitor for inter-metal and metal overlap.  $C_{ox}$  is the capacitor between metal and substrate ground.  $R_{sub}$  and  $C_{sub}$  serve for substrate loss. Using the S parameters derived at the previous step, a set of conversion equations are applied to calculate component values of the equivalent circuit [20].

The next step is to verify the equivalent circuit model by measurements on a manufactured inductor testkey. The actual S parameters are measured. If these parameters have an unacceptable mismatch from the simulation values, perform the second step for these measured parameters to find a convergence.

## 2.2 Simulation and Measurement

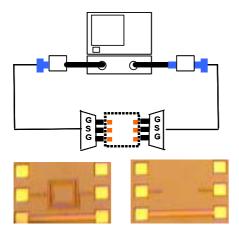

An example of 2.5-turn on-chip rectangular spiral inductor was fabricated by 0.25µm CMOS process. The measurements were performed by using onwafer probing with Agilent 8510 sited on CIC, as shown in Fig.3. Calibration and de-embedding were carefully carried out, respectively.

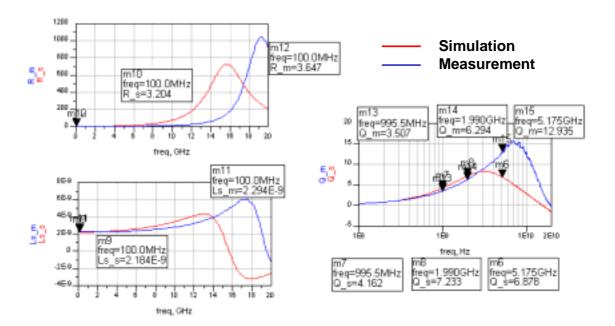

The measurement results compared with simulation results are shown in Fig.4 for  $R_s$ ,  $L_s$  and Q, respectively. From these figures, the measured results outperform simulation ones, we can expect that our simulation model is a little conservative, especially in higher frequency. Since, we are only interested in the 5GHz band, the results are acceptable.

## **3 IPD Inductor Modeling**

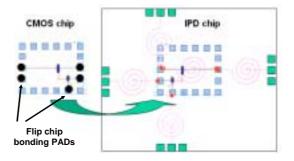

To overcome the inherent substrate loss of CMOS on-chip inductor, integrated passive device (IPD) inductors employing flip chip packaging are developed. Fig.5 is the illustration of multi-chip module packaging. A CMOS circuit chip with active devices and a IPD chip with passive devices are fabricated, and then micro-bump bonding is used to interconnect these two chips.

To use the IPD inductors in RF circuit designs, models of the IPD inductors are needed. Testkeys are fabricated and measured. The measured S parameters are converted to the simulation models

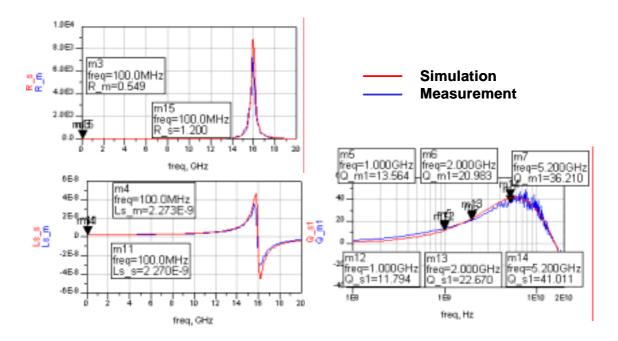

using the steps described in Section 2. Fig.6 is a 3.5-turn IPD inductor. Its measurement results and simulation results are shown in Fig.7 for  $R_s$ ,  $L_s$ , and Q, respectively. The results are well matched. Its Q value is about 40 at 5GHz. Table 1 lists the comparisons of IPD and on-chip inductors. With the same inductor values, IPD inductor has smaller resistance and higher Q value. The area is a little larger than on-chip inductor due to bonding pads, however it is much smaller than off-chip inductor.

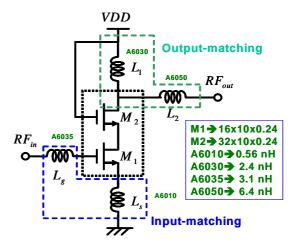

To demonstrate the superiority of IPD inductor over on-chip inductor, two cascode LNAs using different inductor realizations are designed, as shown in Fig.8. The simulation results are listed in Table 1. Operating at the same supply voltage and power consumption, the IPD-inductor LNA has lower NF and higher gain than the on-chip-inductor LNA. The LNAs were submitted to CIC for fabrication.

#### 4 Conclusion

In this paper, an integrated passive device (IPD) inductor modeling is demonstrated. The inductor models are built by measuring S parameters of testkey, and then converting into simulation model. To manifest the superiority of the IPD inductors, the derived models are used to design two cascode LNAs with on-chip and IPD inductors, respectively. The simulation results show that the IPD-inductor LNA has lower NF and much higher gain than the on-chip-inductor LNA. The IPD technology which has high quality passive device and compatible with CMOS process is a promise for RF applications.

Acknowledgement - The authors will give a great thanks to the staffs of Chip Implementation Center (CIC) for their dedicated works on helping the implementation and measurement of the chips. They will also deeply appreciate the helps of Aisa Pacific Microsystem Inc. This work is also sponsored by National Science Council contract NSC-92-2218-E-260-003.

Table 1 Comparisons of IPD and on-chip inductors

| Inductor  | R(Ω) | L(nH) | Q 5.2GHz | Area          | Integration |  |

|-----------|------|-------|----------|---------------|-------------|--|

| On-chip L | 3.42 | 2.17  | 7        | 250μm×300μm   | On-chip     |  |

| IPD L     | 0.54 | 2.27  | 38       | 400 μm×400 μm | Flip-chip   |  |

Table 2 Comparisons of LNAs

| 1              |                |              |            |              |             |             |             |                           |  |  |

|----------------|----------------|--------------|------------|--------------|-------------|-------------|-------------|---------------------------|--|--|

| Cascode<br>LNA | Voltage<br>(V) | Current (mA) | NF<br>(dB) | Gain<br>(dB) | S11<br>(dB) | S12<br>(dB) | S22<br>(dB) | P <sub>1dB</sub><br>(dBm) |  |  |

| On-chip L      | 2.5            | 6.32         | 3.45       | 9.3          | -8.9        | -23.3       | -10.8       | -4                        |  |  |

| IPD L          | 2.5            | 6.32         | 2.37       | 15.2         | -8.5        | -20         | -14         | -10                       |  |  |

#### References:

- [1] J. N. Burghartz, A. E. Ruehli, et al, *Novel Substrate Contact Structure for High-Q Silicon-Integrated Spiral Inductors*, IEEE Electron Devices Meeting, 1997, pp.3.2.1-3.2.4.

- [2] M. Park, S. Lee, et al, *Optimization of High Q CMOS-Compatible Microwave Inductors using Silicon CMOS technology*, IEEE Radio Frequency Integrated Circuits Symposium, 1997, pp.181-184.

- [3] C. P. Yue and S. S. Wong, *On-Chip Spiral Inductors with Patterned Ground Shields for Si-Based RF IC's*, IEEE Journal of Solid-State Circuits, vol. 33, NO.5, 1998, pp.743-751.

- [4] F. Ling, J. Song, et al, Systematic Analysis of Inductors on Silicon Using EM Simulation, IEEE Electronic Components and Technology Conference, 2002, pp.484-489.

- [5] M. Danesh and J. R. Long, *Differentially Driven Symmetric Microstrip Inductors*, IEEE Journal of Transaction on Microwave Theory and Techniques, vol.50, NO.1, 2002, pp.332-341.

- [6] J. Rogers, L. Tan, et al, A High Q On-Chip Cu Inductor Post Process for Si Integrated Circuits, IEEE Interconnect Technology Conference, 1999, pp.239-241.

- [7] S. Jenei, S. Decoutere, et al, *High Q Inductors* and *Capacitors on Si substrate*, Silicon Monolithic Integrated Circuits in RF Systems, 2001, pp.64-70.

- [8] H. Lakdawala, X. Zhu, et al, *Micromachined High-Q Inductors in 0.18um Cu Interconnect Low-K CMOS*, IEEE Custom Integrated Circuits Conference, 2001, pp.152-157.

- [9]J. Sevenhans, F. O. Enyde, and P. Reusens, *The Silicon Radio Decade*, IEEE Trans. on Microwave Theory and Techniques, 2002, pp. 235-244.

- [10]T. H. Lee, *The Design of CMOS Radio-Frequency Integrated Circuit*, Cambridge University Press, 1998.

- [11]M. Rytivaara, *Buried passive elements manufactured in LTCC*, Packaging and Interconnects at Microwave and mm-Wave Frequencies IEE Seminar, 2000, pp.6/1-6/5.

- [12]D. Heo, A. Stutono, et al, A High Efficiency 0.25-um CMOS PA with LTCC Multi-layer High-Q Integrated Passives for 2.4GHz ISM Band, IEEE Microwave Symposium, 2001, pp.915-918.

- [13]A. Iqbal, M. Swaminathan, et al, *Design Tradeoffs Among MCM-C, MCM-D and MCM-D/C Technologies*, IEEE Transactions on Components, Packaging, and Manufacturing Technology, 1994, pp.22-29.

- [14]M. D. Samber, N. Pulsford, et al, Low Complexity MCM-D Technology with Integrated Passive for High Frequency Applications, Multichip Modules and High Density Packaging Conference, 1998, pp.285-290.

- [15]R. G. Arnold, C. C. Faulkner and D. J. Pedder, *Silicon MCM-D Technology for RF Integration*, IEEE Multichip Module Conference, 1997, pp340-344.

- [16]G. Carchon, K. Vaesen, et al, *Multilayer Thin-Film MCM-D for the Integration of Hogh-Performance RF and Microwave Circuits*, IEEE Transactions on Components and Packaging Technology, Vol.24, No.3, 2001 pp.510-519.

- [17]W. Diels, K. Vaesen, et al, Single-Package Integration of RF Blocks for a 5GHz WLAN Application, IEEE Transactions on Advanced Packaging, Vol.24, No.3, 2001, pp.384-391.

- [18]http://www.apmsinc.com/

- [19]C. P. Yue and S. S. Wong, *Physical Modeling of Spiral Inductors on Silicon*, IEEE Transactions on Electron Devices, vol.47, NO.3, 2000, pp.560-568.

- [20]C. P. Yue, C. Ryu, et al, A Physical model for planar spiral inductors on silicon, IEEE Electron Devices Meeting, 1996, pp.6.5.1-6.5.4.

Fig.1 A 2.5-turn spiral on-chip inductor

Fig.2 Equivalent circuit of on-chip inductor

Fig.3 The measurement setup and chip photos

Fig.5 The flip-chip microbump bonding

Fig.6 The IPD inductor

Fig.8 The Cascode LNA

Fig.4 Measurement and simulation results of on-chip L

Fig.7 Measurement and simulation results of IPD L